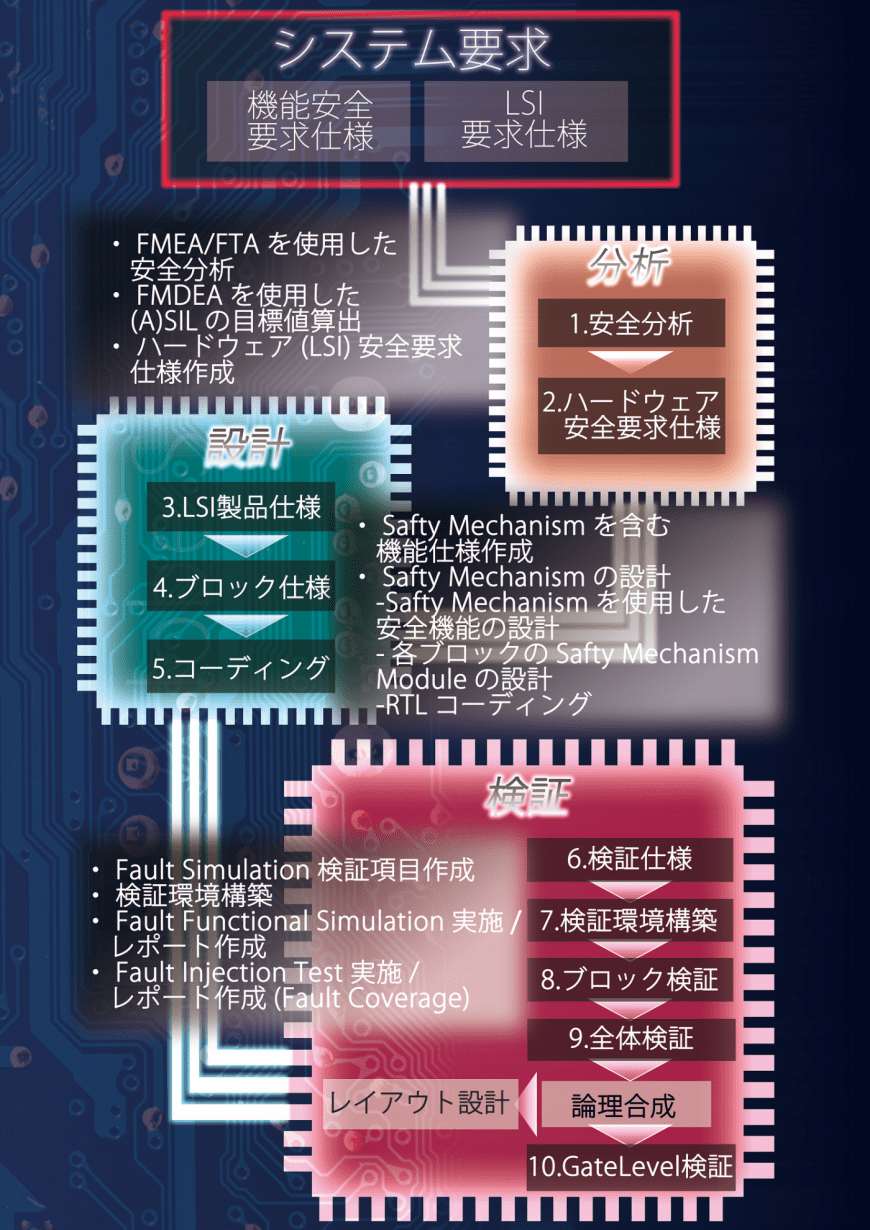

機能安全工程

「分析」工程

「分析」工程は、機能安全のLSI開発を行う際に最初に行う工程になります。エンドユーザの機能安全要求に対して、LSIのリスクを見える化する工程です。

実施内容

- 機能不全が発生しない網羅性の高い安全分析項目を作成します。

- 外部ハザード及び内部ハザード要因を明確化し、LSI要求仕様及びアーキテクチャに沿ったリスク評価を行い、蓄積されたアプリケーションノウハウを活かしリスクに対して無駄のない安全方策を決めます。

- LSI要求仕様と安全方策からオーバースペックのないハードウェア安全要求(LSI安全要求)を作成します。また、SoC/SoC FPGAの場合は、ソフトウェア安全要求も併せて作成します。

「設計」工程

「設計」工程は、ハードウェア安全要求とLSI要求仕様から、エンドユーザーの機能安全要求と機能安全規格に対応したLSI開発要求仕様を作成し、安全機構を含むアーキテクチャー設計、論理設計及びRTLコーディングを行う工程です。

見える化したリスクに対して、リスクを制御するLSIの仕様と機能を見える化する工程です。

実施内容

- エンドユーザーの開発システムの安全要求機能に対して、LSIの動作として機能漏れが発生しないLSI開発要求仕様を作成します。

- 開発するLSIのデータ処理機構に合わせた機能不全が発生しないSafety Mechanism要求仕様を作成します。

- LSIのブロック構成及びブロックの各機能に適した回路規模が最小となるSafety Mechanismを設計します。

- 故障検出率の向上させるRTLをコーディングします。

「検証」工程

「検証」工程は、LSI開発要求仕様に基づき、設計したRTLに対して機能検証を行い、ゲート回路に対して故障検出率を算出します。

設計したRTLが機能安全規格の規定を満たしていることを証明する工程です。

設計結果に対して安全性を見える化する工程であり、コストが一番発生する工程です。

機能安全の知見と検証技術の両方を合わせ持つことによって、コストダウンを図ることができます。

実施内容

- 機能安全に対応した検証効率の高い検証項目を作成します。

- Fault Coverage漏れが発生しないSimutation環境を構築します。

- ツール経験豊富な検証エンジニアが、イタレーションが発生しないFault Injection Simulation環境の構築とFault Injection Simulationを行います。